您现在的位置是:首页 > 电路图 > 电机控制电路 > 电机控制电路

高精度回声数据采集模块的设计

![]() 转载来源:电子技术应用-AET chinaaet.com 电子发烧友 elecfans.com2017-03-23

转载来源:电子技术应用-AET chinaaet.com 电子发烧友 elecfans.com2017-03-23

简介吴松 (中船重工集团第七二六所,上海 201100) 摘要:介绍了一种基于Σ-Δ型24位模数转换器的采集系统,系统实现增益0~60 dB可调节,输入信号几微伏到几十毫伏的高精度采集,多种频

吴松

(中船重工集团第七二六所,上海 201100)

摘要:介绍了一种基于Σ-Δ型24位模数转换器的采集系统,系统实现增益0~60 dB可调节,输入信号几微伏到几十毫伏的高精度采集,多种频率的滤波输出;采用FPGA实现对模数转换器的配置、控制和数据读取,采集的大量数据缓存到外部Flash,由DSP读取并进行FIR滤波处理后通过RS422接口发送到主机进行回波识别。

关键词:Σ-Δ型、高精度采集、FPGA、DSP

0引言

伴随着电子技术的高速发展,应用领域的不断拓宽,使得连接模拟世界与数字世界桥梁的模数转换器显得格外重要,同时对模数转换器的性能也提出了更高的要求。回声信号非常微弱,最小只有几个微伏,还夹杂着各种干扰信号,为了从干扰信号中检测出有效信号,同时满足系统高精度与响应时间的要求,本文介绍一种基于Σ-Δ型高精度ADC的采集模块,满足了系统的性能要求。

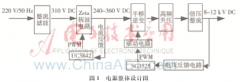

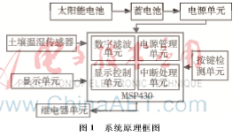

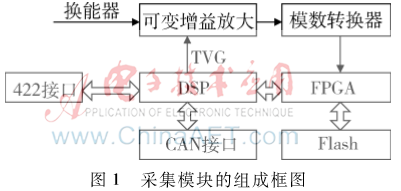

1数据采集模块整体结构

采集模块的组成框图如图1所示,主要由可变增益放大器、模数转换器、FPGA、DSP、Flash、422接口和CAN接口组成。换能器接收到的微弱信号,经放大器放大到AD模拟输入范围内的差分输入信号;模数转换器将可变增益放大器输出的差分信号转换为数字信号,经过完全滤波后输出数字量;FPGA控制模数转换器的读写时序,读入转换的数据并完成缓存与处理,然后将数据存到外接Flash存储器;DSP通过FPGA配置AD的采样速率,控制采样时间,调节可变增益放大器的增益,读取Flash的数据进行滤波处理,然后通过通信接口将数据发送给主机。

2系统硬件设计

2.1主要器件选型

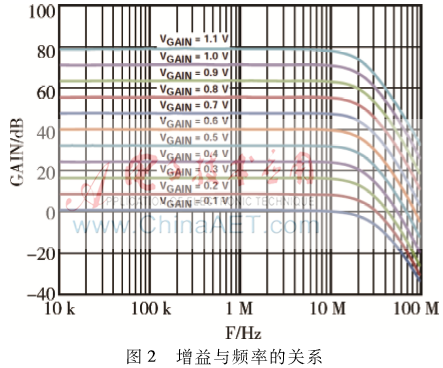

本文介绍的回声信号是由发射换能器向海底定向发射声波,到达海底后返回形成的一种夹杂着各种噪音的声波信号,接收换能器将某一固定频率附近的回声信号转化为电压信号。由于不同的水深需要发射的声波强弱不同,所以回波的强弱也不同,相应转化成的电压信号从几微伏到几十毫伏不等,所以要求放大电路具有低噪音和可变的增益。AD8338是一种可变增益放大器(VGA),适合要求全差分信号路径、低功耗、低噪声和在LF~18 MHz频段内具有精确增益的应用,基本增益函数为线性的,标称增益范围为0 dB~80 dB;标称增益范围与增益引脚上0.1 V~1.1 V的控制电压相对应,增益与频率的关系如图2所示。

AD8338只需几个分立器件,用户就可以自定义该器件的增益、带宽、输入阻抗及噪声性能,以满足自身应用的需求。器件采用3.0 V~5.0 V的单电源供电,能效极高,仅消耗低至3 mA的静态电流。

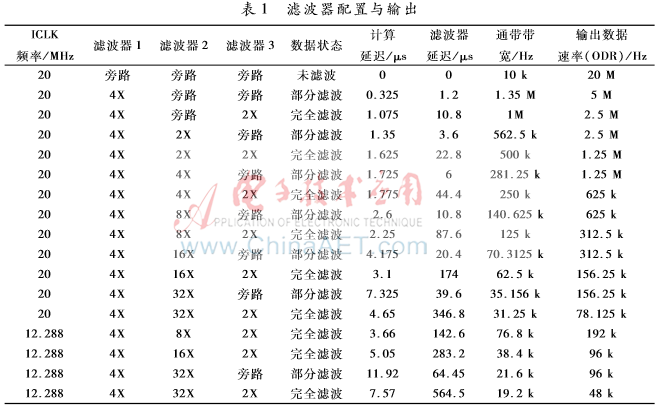

AD7760是一款高性能、24位Σ-Δ型模数转换器,融合了宽输入带宽和高分辨率的特性,以2.5 MHz的频率输出数据时信噪比(SNR)达100 dB,动态范围也为100 dB。接收换能器输出的信号动态范围宽,经可变增益放大器AD8338放大后输出的差分信号峰峰值为2.8 V,而AD7760的差分输入电压的峰峰值为3.25 V,满足了动态范围和差分模拟输入的要求。此外AD7760内置用于信号缓冲和电平转换的差分放大器、超量程标志、内部增益与失调寄存器以及低通数字滤波器,器件提供可编程的抽取率,3个串联FIR滤波器,抽取比、滤波器选择和旁路有许多种不同的组合,因此能以多种数据速率输出数据,范围从48 kHz~2.5 MHz,可以满足不同条件下对信号输出速率的要求,如表1所示。

器件的输入同步引脚也为应用提供了便利,允许用户从一个已知的时间点采集模拟前端输入的样本,因此发射换能器的发射波结束后,处理器可以精确地控制模数转换器开始采集的时间节点。AD7760对于要求高信噪比的应用来说,还可以简化对前端信号调理电路的要求,从而降低了模拟电路的复杂度。

2.2采集电路设计

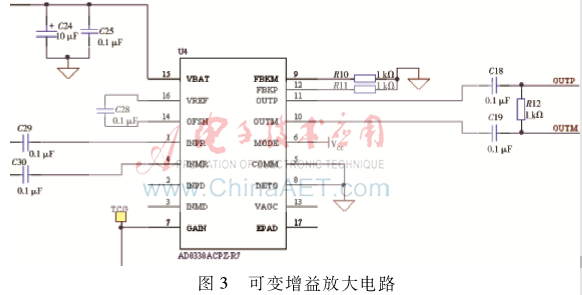

采集电路由一片可变增益放大器AD8338、一片模数转换器AD7760和一片FPGA组成。处理器通过调节AD8338的GAIN引脚上的电压(0.1 V~1.1 V)来实现放大器0~80 dB的增益调节,差分信号通过引脚OUTP和OUTM输出,可变增益放大电路如图3所示。

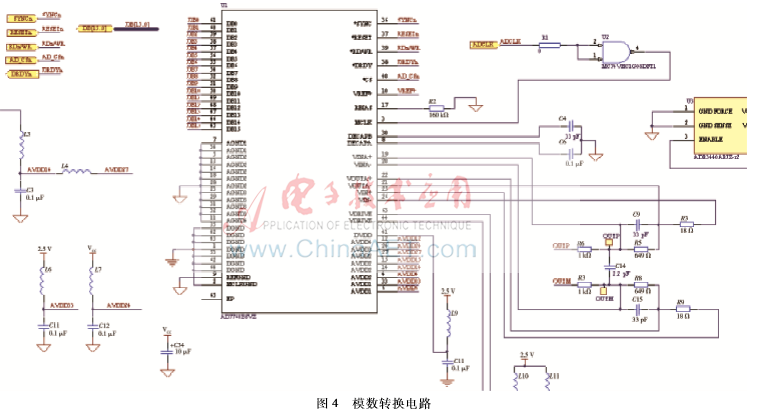

要实现AD7760如上所述的高性能,必须采用适当的去耦和布局技术,尤其对电源输入有着较为严格的要求,每个电源引脚必须通过铁氧体磁珠连接到适当的电源,并用一个100 nF的电容去耦至正确的接地引脚,AD7760的基准电压也要由专用的低噪音基准电压源提供。AD7760需要一个外部低抖动时钟源,而且输入时钟信号必须经过缓冲之后才能输入器件的MCLK引脚,所以需要将FPGA产生的40 MHz的时钟信号经过与门的两个输入端,然后将与门的输出接到器件的MCLK引脚。模数转换电路如图4所示。

FPGA与AD7760之间的信号线主要有双向数据总线、芯片复位线、片选、读写控制、同步信号和数据就绪输出信号。复位线可以复位模数转换器内部的数字电路;同步信号的下降沿可以使内部滤波器复位;数据就绪输出信号是一个低电平的脉冲信号,表示数据总线上有数据输出;读写控制、片选和双向数据总线完成对模数转换器的内部寄存器的配置和读取滤波输出的数据。

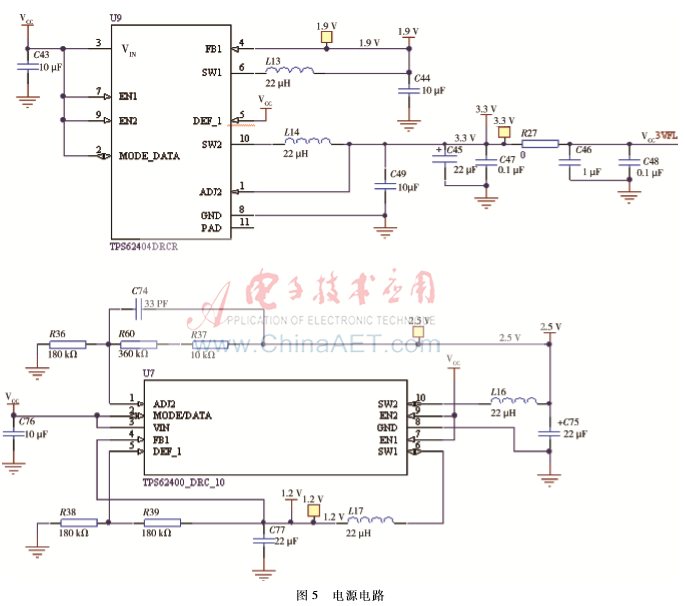

2.3电源电路设计

采集模块是单电源5 V供电,系统内部FPGA的内核供电电压是1.2 V,IO供电电压是3.3 V,AD7760使用2.5 V和5 V两种电源供电,DSP内核供电电压为1.9 V,IO供电电压3.3 V。FPGA和DSP属于低功耗器件,实际使用中的功耗大约是300 mW,而AD7760正常工作状态下的功耗接近1 W。实验中使用线性电源发现:由于电路正常工作的功耗较大,而线性电源转换效率低,导致整个系统正常工作中功耗更高,电源芯片发热严重,不利于严苛条件下系统的稳定工作,所以实际使用中采用了开关电源。开关电源具有体积小、功耗低、转换效率高、稳压范围宽、滤波效率高、安全可靠和电路形式灵活等优点。电路中使用TI公司的TPS62400和TPS62404,输入电压范围2.5~6 V,可调节的电压输出范围是0.6 V~VIN,转换效率高达95%,误差范围仅为1%,输出的电流为400 mA和600 mA,满足了系统对电源的性能要求,电源电路如图5所示。

3系统软件设计

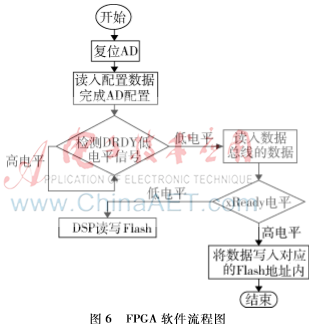

系统软件主要包括FPGA软件和DSP软件两部分,FPGA软件实现对AD7760的控制、数据读取缓存和读写Flash;DSP软件完成对AD7760的间接配置、数据读取与处理和数据发送。FPGA软件流程如图6所示。

AD7760的软件初始化包括启动时钟振荡器、复位信号拉低并至少保持一个时钟周期、复位信号释放并至少保持两个时钟周期、写入控制寄存器2地址和数据设置时钟分频比、写入控制寄存器1地址和数据设置输出数据速率、片选释放并至少等待5个时钟周期。配置完成后释放同步信号,模数转换器开始工作,软件开始检测数据准备就绪信号DRDY,检测到低电平脉冲时开始读取数据总线上的数据,数据传输使用16位双向并行接口,24位转换数据以二进制补码形式输出,所以读取一次转换结果要执行两次16位读操作,第二次读操作输出转换结果的低8位和6个状态位。读取转换结果后检测DSP空闲标志位,空闲状态将结果写入Flash对应的地址内,一次工作周期结束后给DSP一个完成信号。开始工作后,DSP将模数转换器的配置数据写入外接Flash,给发射机提供一个脉冲信号控制发射机的发射时间,结束后释放模数转换器的同步信号,开始进行回波的采集,采集一次完整的回波信号后,DSP将数据全部读入内部缓存区,并进行数据FIR滤波与处理,然后通过RS422接口发送给主机进行回波识别。

4结论

通过模块调试后系统性能达到了预期的要求,AD7760能够实现预期的多种频率滤波数据输出,增益0~60 dB可调节,FPGA的外接时钟50 MHz,综合后进行静态时序分析,最高工作频率可以达到242 MHz,满足时序要求,系统总体功耗在2 W左右。将回波采集模块加到整机上进行测试,整机工作正常,在多个量程下进行水深实测,均满足1%的误差要求,增益范围可调,系统工作稳定可靠,对比之前设备的采集模块,简化了模拟电路部分的设计,提高了精度和性噪比,采样速率大幅提高,从而提高了整个设备的精度。

参考文献

[1] Analog Devices. AD8338. Low Power,18 MHz Variable Gain Amplifier[Z]. 2013:1-20.

[2] Analog Devices. AD7760.2.5 MSPS,24Bit,100 dB SigmaDelta ADC with On Chip Buffer[Z].2006:1-36.

[3] Analog Devices. ADM3053.Signal and Power Isolated CAN Transceiver with Integrated Isolated DC to DC Converter[Z].2013:1-20.

[4] Analog Devices. ADM2582E. Signal and Power Isolated RS 485 Transceiver with ±15 kV ESD Protection[Z].2014:1-20.

[5] Texas Instruments. TPS6240xQ1 2.25 MHz 400mA and 600 mA Dual Step Down Converter[Z].2014:1-41.

[6] 侯伯亨,刘凯,顾新.VHDL硬件描述语言与数字逻辑电路设计(第三版)[M].西安:西安电子科技大学出版社,2009.

[7] 王成华,王友仁,胡志忠,等.电子线路基础[M].北京:清华大学出版社,2008.

[8] WAITE A D.实用声纳工程[M].王德石,译.北京:电子工业出版社,2004.

[9] EDA先锋工作室.Altera FPGA/CPLD设计(基础篇)[M].王诚,吴继华,等译.北京:人民邮电出版社,2005.