您现在的位置是:首页 > 电气技术 > 电气技术

运放比例放大电路及高输入阻抗电路图

![]() 来源:艾特贸易2017-03-18

来源:艾特贸易2017-03-18

简介电路中需要将15V+的待测电压,输入到+5V的差分运放ADS1274中。ADC的参考电压是+2.5V,测量范围是-2.5V~+2.5V。 首先需要一个差分运放来实现单端转差分以及比例缩小。输入侧将负端通过Ri

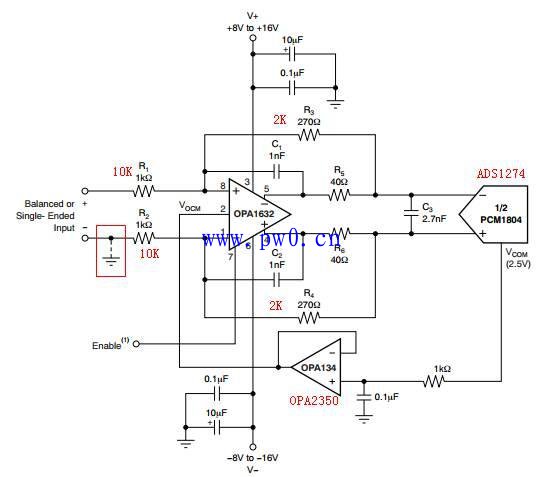

电路中需要将15V+的待测电压,输入到+5V的差分运放ADS1274中。ADC的参考电压是+2.5V,测量范围是-2.5V~+2.5V。

首先需要一个差分运放来实现单端转差分以及比例缩小。输入侧将负端通过Rin电阻接地,正端接测量信号。差分运放比较容易实现准确的比例缩小,Rin=10K,Rf=2K,Gain=1/5,缩小5倍。(如果是普通运放则需要在输入端用电阻分压来实现缩小,但在下面的高输入阻抗场合是完全不可取的)

差分输出偏置在2.5V左右,来自于后端的ADC,这个不需要精确。考虑到多个OPA共用这个偏置,中间用OPA2350运放跟随一下。完全可以在OPA2350上设置分压或放大,来产生其他偏置电压。

前端有四路待测信号,都通过一个10K电阻接到1632的正端,某个时间内只有一路通过开关导通到OPA。

其中有三路信号的驱动能力都是mA级的,另一路是uA级的弱电流。

OPA1632的输入偏置电流(Input Bias Current)要求2uA左右,所以mA级信号驱动它是不会有问题的。但是前端如果就是uA级电流来驱动,怕是不能保证放大器工作在线性范围。实测uA级信号过来会直接被1632拉到偏置电压附近,完全偏离。

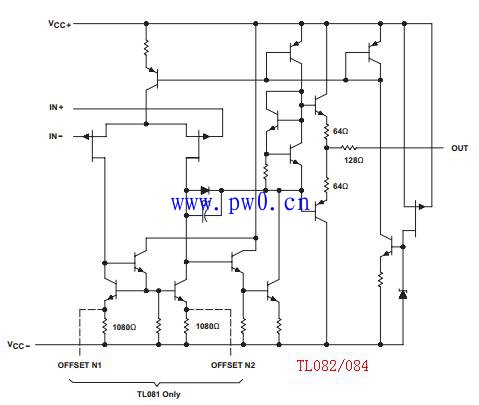

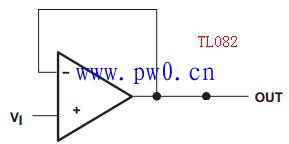

这时就需要在前级加一个更高输入阻抗的运放来buffer一下。FET型的一般输入阻抗都非常大,这里选择常用的TL082,J-FET输入管,阻抗是10的12次方欧姆。偏置电流都是pA或nA级别的,弱电流也能轻松驱动。

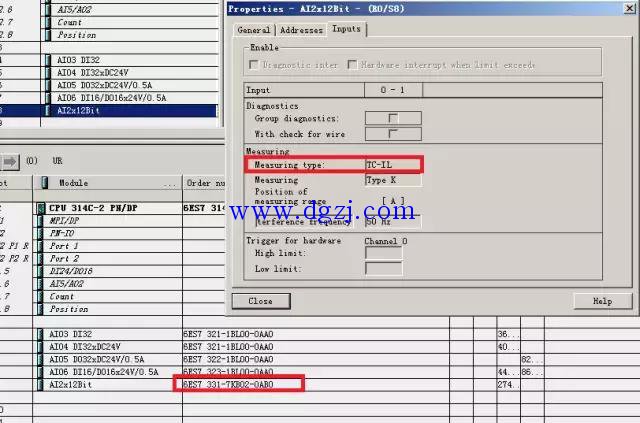

下面是两个OPA的内部结构图

在搭电路的时候犯错了。信号先通过Relay继电器,然后到TL082跟随。结果Relay切开之后,输入Vin悬空!!!这时候输出电压就不受控了,可能是浮动也可能由内部结构决定输出电压值,实测是-3.5V(负轨是-5V电)。

解决措施就是把开关Relay放到TL082后面,输出可以悬空,但输入不能。

另外关于双电源供电是否要对称的问题,我这里正电源是+15V,负电源是-5V,只要在供电范围内,其实不需要完全对称。

上述的两路OPA都是采用同相放大,所以有共模干扰的考虑,单端线路尽量短,参考要好,让差分来走长路径。

点击排行

室内风扇电机和霍尔元件的检测

室内风扇电机和霍尔元件的检测